Why Adaptive Testing is Important in Test Technology

The Quiet Work Behind Every Successful Chip

Revenue is the lifeblood of any business. The harsh reality is that no matter how innovative your product, how illustrious your investors are, or how astronomical your market valuation is, your business won't survive without the ability to generate income. Similarly, in semiconductor manufacturing, testing is the lifeblood that ensures every chip functions reliably before reaching consumers.

Every phone call, video stream or cloud request runs on silicon that's been tested, again and again, until it earned trust. Testing isn't fancy and glamorous, but it's what turns a design into a reliable product. It's the step between "it works on paper" and "it works in the real world."

Yet one small detail often makes a big difference: how long testing takes.

In high-volume manufacturing, shaving even a tenth of a second off each chip's test time adds up to millions in savings. The funny thing is, test time rarely gets the spotlight. But it drives cost, affects throughput, and even shapes how quickly new products reach the market.

Why Engineers Care About Test Time

Product engineers live somewhere between design and manufacturing. Their job is to make sure a chip isn't just functional but also manufacturable and testable at scale.

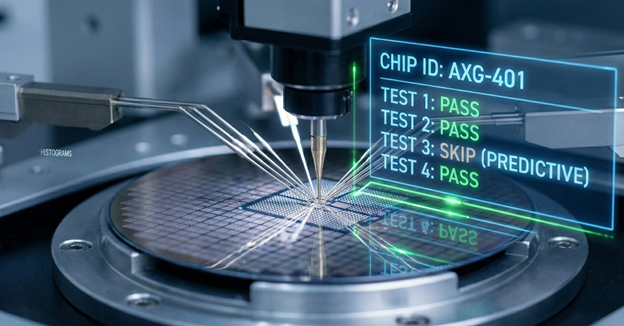

Every die goes through automated testers that run functional, parametric and reliability checks. The process weeds out defects and validates performance across voltage and temperature corners.

The math is simple: longer tests cost more money and slow down everything that follows. Optimizing test time can speed up yield learning, improve equipment use and shorten the path from tape out to volume ramp. The catch is that cutting test time without losing coverage takes both insight and restraint.

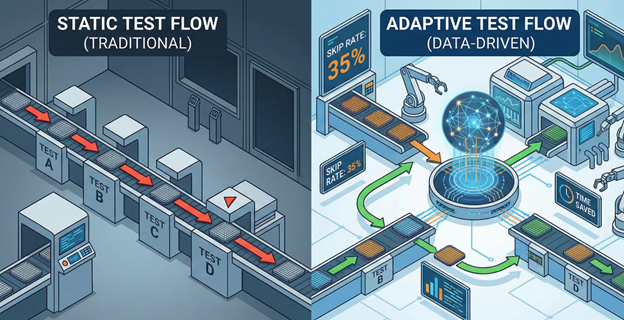

The Old Way: Static Test Flows

For a long time, testing was static. Engineers compacted patterns, removed redundancy and sent every chip through the same fixed sequence. It worked, mostly.

Static test programs are predictable. They're easy to maintain and offer solid fault coverage. But they don't adapt. Even a perfect die spends time running checks it doesn't need. When you're shipping in the millions, that wasted time becomes expensive.

A Smarter Approach: Adaptive Testing

Adaptive testing changes that rhythm. Instead of following a single path, it decides which tests to run based on earlier results. The flow adjusts itself.

It starts with data. Engineers look at historical test logs, identify correlations and figure out which patterns tend to fail together. The system then runs the most failing tests first. If those pass, it can safely skip others. The whole thing runs faster without losing reliability.

Metrics like skip histograms and per device test time charts help track progress. In practice, adaptive methods often match or beat traditional coverage while cutting total test time by a noticeable margin.

Where Hardware Meets Data

What's striking now is how much software has entered the test floor. Ten years ago, optimization meant tweaking pin timings or voltage margins. Now, it might involve Python scripts, yield dashboards or a bit of machine learning.

Engineers study data from thousands of wafers, hunting for patterns. Some predict yield shifts; others refine which tests to keep. It's not about replacing engineering judgment—it's about giving it better evidence to work with.

This shift has quietly blurred the old boundaries between hardware and software roles. The best test engineers today can read data as fluently as they read schematics.

Scaling the Impact

Once an optimized test flow works in one line, it can scale everywhere. A five percent drop in average test time doesn't sound like much until you realize what it means in factory terms: more wafers processed, better tool use, less power consumed, fewer devices stressed during test.

It also helps with faster product launches. Adaptive test flows can be updated or tuned midstream instead of being rebuilt from scratch.

Looking Ahead

The next big leap might come from connecting the dots between design, fab and test. Imagine test systems that learn from yield data and adjust automatically for each silicon revision.

We're already seeing steps in that direction: data flowing both ways, algorithms suggesting tweaks and test programs that get smarter the longer they run.

It's not about replacing engineers. It's about giving them better visibility and more control.

Conclusion

In chip manufacturing, time isn't just money—it's feedback. Every second saved on the tester gives engineers more room to experiment, iterate and improve.

Test time might seem like a small metric buried deep in factory reports, but it quietly drives innovation forward. The better we understand it, the faster the industry moves.

[story continues]

tags